双极性晶体管

此條目需要补充更多来源。 (2016年9月23日) |

双极性電晶體(英語:bipolar transistor),全称双极性结型晶体管(bipolar junction transistor, BJT),俗称三极管,是一种具有三个终端的电子器件。双极性晶体管是电子学历史上具有革命意义的一项发明,[1]:79其发明者威廉·肖克利、约翰·巴丁和沃尔特·布喇顿被授予1956年的诺贝尔物理学奖。[2]

这种晶体管的工作,同时涉及电子和空穴两种载流子的流动,因此它被称为双极性的,所以也稱雙極性載子電晶體。这种工作方式与诸如场效应管的单极性晶体管不同,后者的工作方式仅涉及单一种类载流子的漂移作用。两种不同掺杂物聚集区域之间的边界由PN结形成。[3]:95

双极性晶体管由三部分掺杂程度不同的半导体制成,晶体管中的电荷流动主要是由于载流子在PN结处的扩散作用和漂移运动。以NPN電晶體為例,按照设计,高掺杂的发射极区域的电子,通过扩散作用运动到基极。在基极区域,空穴为多数载流子,而电子少数载流子。由于基极区域很薄,这些电子又通过漂移运动到达集电极,从而形成集电极电流,因此双极性晶体管被归到少数载流子设备。[4]:30[5]:35

双极性晶体管能够放大信号,并且具有较好的功率控制、高速工作以及耐久能力,[6]:48,所以它常被用来构成放大器电路,或驱动扬声器、电动机等设备,并被广泛地应用于航空航天工程、医疗器械和机器人等应用产品中。[6]:48

通斷(傳遞訊號)時的雙極晶體管表現出一些延遲特性。大多數晶體管,尤其是功率晶體管,具有長的儲存時間,限制操作處理器的最高頻率。一種方法用於減少該存儲時間是使用Baker clamp。

发展及应用

[编辑]1947年12月,贝尔实验室的约翰·巴丁、沃尔特·布拉顿在威廉·肖克利的指导下共同发明了点接触形式的双极性晶体管。[7]1948年,肖克利发明了采用结型构造的双极性晶体管。[8]在其后的大约三十年时间内这种器件是制造分立元件电路和集成电路的不二选择。

早期的晶体管是由锗制造的。在1950年代和1960年代,锗晶体管的使用多于硅晶体管。硅晶体管截止电压通常为0.5至 1V,锗晶体管的截止电压更小,通常约0.2V,这使得锗晶体管适用于某些应用场合例如高灵敏度的设备。在晶体管的早期历史中,曾有多种双极性晶体管的制造方法被开发出来。[9]

锗晶体管的一个主要缺点是它容易产生热失控。[10]由于锗的禁带宽度较窄[11],如果要稳定工作,則对其工作温度的要求相对硅半导体更嚴[10],因此大多数现代的双极性晶体管是由硅制造的[12]。採用矽的另外一個原因是容易形成穩定的二氧化矽,二氧化矽與其他金屬之間的粘性也大,容易製作電子器件[13]。

后来,人们也开始使用以砷化镓为代表的化合物来制造半导体晶体管。砷化镓的电子迁移率为硅的5倍,[14]用它制造的晶体管能够达到较高的工作频率。此外,砷化镓热导率较低,有利于高温下进行的加工。[14]化合物晶体管通常可以应用于高速器件。[來源請求]

双极性晶体管能够提供信号放大,它在功率控制、模拟信号处理等领域有所应用。此外,由于基极-发射极偏置电压与温度、电流的关系已知,双极性晶体管还可以被用来测量温度。[15]根据基极-发射极电压与基极-发射极和集电极-发射极电流的对数关系,双极性晶体管也能被用来计算对数或求自然对数的幂指数。[來源請求]

随着人们对于能源问题的认识不断加深,场效应管(例如互補式金屬氧化物半導體)技术凭借更低的功耗,在数字集成电路中逐渐成为主流,双极性晶体管在集成电路中的使用由此逐渐变少。[6]:48-49但是应当看到,即使在现代的集成电路中,双极性晶体管依然是一种重要的器件,市场上仍有大量种类齐全、价格低廉的晶体管产品可供选择。与金属氧化物半导体场效应晶体管相比,双极性晶体管能提供较高的跨导和输出电阻,并具有高速、耐久的特性,在功率控制方面能力突出。[6]:48因此,双极性晶体管依旧是组成模拟电路,尤其是甚高频应用电路(如无线通信系统中的射频电路)的重要配件。双极性晶体管可以通过BiCMOS技术与和MOSFET制作在一块集成电路上,这样就可以充分利用两者的优点(如双极性晶体管的电流放大能力和场效应管的低功耗特点)。[6]:53-54

基本原理

[编辑]

NPN型双极性晶体管可以视为共用阳极的两个二极管接合在一起。在双极性晶体管的正常工作状态下,发射结(基极与发射极之间的PN结)处于正向偏置状态,而集电结(基极与集电极之间的PN结)则处于反向偏置状态。[4]:29-30在没有外加电压时,发射结N区的电子(该区域的多数载流子)浓度大于P区的电子浓度,部分电子将扩散到P区。同理,P区的部分空穴也将扩散到N区。这样,发射结上将形成一个空间电荷区(也称为耗尽层),产生一个内在的电场,其方向由N区指向P区,这个电场将阻碍上述扩散过程的进一步发生,从而达成动态平衡。[16]:161-162这时,如果把一个正向电压施加在发射结上,上述载流子扩散运动和耗尽层中内在电场之间的动态平衡将被打破,这样会使热激发电子注入基极区域。在NPN型晶体管里,基区为P型掺杂,这里空穴为多数掺杂物质,而电子则为少数载流子。[來源請求]

从发射极被注入到基极区域的电子,一方面与这里的多数载流子空穴发生复合,另一方面,由于基极区域掺杂程度低、物理尺寸薄,并且集电结处于反向偏置状态,大部分电子将通过漂移运动抵达集电极区域,形成集电极电流。[3]:35为了尽量缓解电子在到达集电结之前发生的复合,晶体管的基极区域的厚度必须远小于电子的扩散长度(diffusion length,参见菲克定律),使得载流子扩散所需的时间短于半导体少数载流子的寿命。在现代的双极性晶体管中,基极区域厚度的典型值为十分之几微米。[17]:347需要注意的是,集电极、发射极虽然都是N型掺杂,但是二者掺杂程度、物理属性并不相同,因此必须将双极性晶体管与两个相反方向二极管串联在一起的形式区分开来。[5]:33-34

分析方法

[编辑]集电极-发射极电流可以视为受基极-发射极电流的控制,这相当于将双极性晶体管视为一种“电流控制”的器件。还可以将它看作是受发射结电压的控制,即将它看做一种“电压控制”的器件。事实上,这两种思考方式可以通过基极-发射极结上的电流电压关系相互关联起来,而这种关系可以用PN结的电流-电压曲线表示。[18]

从基极区域的少数载流子浓度出发,可以解释集电极的载流子流动。[18][19][20]:12如果双极性晶体管为小注入,即通过某些物理过程(如光注入或电注入)引入的非平衡载流子(excess carrier,或称“过剩载流子”)比热平衡时的多数载流子少得多,[16]:126-127双极性扩散(即非平衡多数载流子和少数载流子以相同速率流动)速率实际上由非平衡少数载流子决定。另外,双极性晶体管处理高频信号的能力还受限于基极区域载流子的渡越时间。[20]:12

人们曾经建立过多种数学模型,用来描述双极性晶体管的具体工作原理。例如,古梅尔–潘模型(Gummel–Poon Model)提出,可以利用电荷分布来精确地解释晶体管的行为。[21]上述有关电荷控制的观点可以处理有关光电二极管的问题,这种二极管基极区域的少数载流子是通过吸收光子(即上一段提到的光注入)产生的。电荷控制模型还能处理有关关断、恢复时间等动态问题,这些问题都与基极区域电子和空穴的复合密切相关。然而,由于基极电荷并不能轻松地在基极引脚处观察,因此,在实际的电路设计、分析中,电流、电压控制的观点应用更为普遍。[來源請求]

在模拟电路设计中,有时会采用电流控制的观点,这是因为在一定范围内,双极性晶体管具有近似线性的特征。在这个范围(下文将提到,这个范围叫做“放大区”)内,集电极电流近似等于基极电流的倍,这对人们分析问题、控制电路功能有极大的便利。在设计有的基本电路时,人们假定发射极-基极电压为近似恒定值(如),这时集电极电流近似等于基极电流的若干倍,晶体管起电流放大作用。[來源請求]

然而,在真实的情况中,双极性晶体管是一种较为复杂的非线性器件,如果偏置电压分配不当,将使其输出信号失真。此外,即使工作在特定范围,其电流放大倍数也受到包括温度在内的因素影响。为了设计出精确、可靠的双极性晶体管电路,必须采用电压控制的观点(例如后文将讲述的艾伯斯-莫尔模型)。[18]电压控制模型引入了一个指数函数来描述电压、电流关系,在一定范围内,函数关系为近似线性,可以将晶体管视为一个电导元件。这样,诸如差动放大器等电路的设计就简化为了线性问题,所以近似的电压控制观点也常被选用。对于跨导线性(translinear)电路,研究其电流-电压曲线对于分析器件工作十分关键,因此通常将它视为一个跨导与集电极电流成比例的电压控制模型。[來源請求]

目前,晶体管级别的电路设计主要使用SPICE或其他类似的模拟电路仿真器进行,[17]:300-302因此对于设计者来说,模型的复杂程度并不会带来太大的问题。但在以人工分析模拟电路的问题时,并不总能像处理经典的电路分析那样采取精确计算的方法,因而采用近似的方法是十分必要的。[5]:3

主要参数

[编辑]电流放大参数

[编辑]

发射极扩散到基极的电子,大部分都能够漂移到集电极,剩下的电子与基极区域的空穴发生载流子复合。成功抵达集电极的电子浓度占发射极扩散出来的电子总浓度的比值,是衡量双极性晶体管效率的一项重要指标。由于发射极区域为重掺杂,基极区域为轻掺杂,所以从发射极被注入到基极的电子浓度大于从基极注入到发射极的空穴浓度。下面将讨论双极性晶体管在电路中以发射极或基极为公共端时的电流放大倍数。

如果晶体管采用共射极接法,输入电流为基极电流,输出电流为集电极电流,当发射结正向偏置、集电结不施加偏置时,晶体管的共射极直流短路电流增益可以表示为集电极电流与基极电流的比值[1]:85

如果集电极从无偏置变为反向偏置,那么与的比值称为共射极静态电流增益,它的表达式为[1]:85

对于小信号模型中的晶体管,的数值通在20到200之间,[5]:36不过在一些为高功率应用设计的晶体管中,它可能会更小一点。

如果晶体管采用共基极接法,输入电流为发射电流,输出电流为集电极电流,当发射结正向偏置、集电结不施加偏置时,晶体管的共基极直流短路电流增益可以表示为集电极电流与发射极电流的比值[1]:84-85

如果集电极从无偏置变为反向偏置,那么与的比值称为共基极静态电流增益,它的表达式为[1]:84-85

上述两个参数可以通过下面的公式相互转换(在NPN型晶体管中)[4]:32

当对低频的交流小信号进行近似分析时,也可以采用上述直流参数。[4]:34如果需要更高的精确度,就必须虑及双极性晶体管中的结电容效应带来的影响。当信号电压的频率达到一定程度后,电流的放大倍数将会下降。[4]:35

功率参数

[编辑]双极性晶体管的最大集电极耗散功率是器件在一定溫度與散热条件下能正常工作的最大功率。在条件相同的情况下,如果实际功率大于这一数值,晶体管的温度将超出最大許可值,使器件性能下降,甚至造成物理损坏。[4]:35[1]:147

极限电流和极限电压

[编辑]当集电极电流增大到一定数值后,虽然不会造成双极性晶体管的损坏,但是电流增益会明显降低。为了使晶体管按照设计正常工作,需要限制集电极电流的数值。除此之外,由于双极性晶体管具有两个PN结,因此它们的反向偏置电压不能够过大,防止PN结反向击穿。[4]:35-36双极性晶体管的数据手册都会详细地列出这些参数。[來源請求]

当功率双极性晶体管集电极的反向偏置电压超过一定数值,并且流经晶体管的电流超出在一定允许范围之内,使得晶体管功率大于二次击穿临界功率就会产生一种被称为“二次击穿”的危险现象。在这种情况里,超出设计范围的电流将造成器件内部不同区域的局部温度不均衡,部分区域的温度高于其他区域。因为掺杂的硅具有负的温度系数(temperature coefficient),所以当它处于较高的温度时,其导电性能更强。这样,较热部分就能传导更多的电流,这部分电流会产生额外的热能,造成局部温度将超过正常值,以致于器件不能正常工作。二次击穿是一种热失控,一旦温度升高,电导率将进一步提升,从而造成恶性循环,最终严重损毁晶体管的结构。整个二次击穿过程只需要毫秒或微秒量级的时间就可以完成。[1]:151

如果双极性晶体管集电结提供超出允许范围的反向偏置,并不对流经晶体管的电流进行限制,发射结将发生雪崩击穿,也会造成器件损坏。[4]:16

温度漂移

[编辑]作为一种模拟的器件,双极性晶体管的所有参数都会不同程度地受温度影响,特别是电流增益。据研究,温度每升高1摄氏度,大约会增加0.5%到1%。[5]:41

抗辐射能力

[编辑]双极性晶体管对电离辐射较为敏感。如果将晶体管置于电离辐射的环境中,器件将因辐射而受到损害。产生损害是因为辐射将在基极区域产生缺陷,这种缺陷将在能带中形成复合中心(recombination centers)。这将造成器件中起作用的少数载流子寿命变短,进而使晶体管的性能逐渐降低。NPN型双极性晶体管由于在辐射环境中,载流子的有效复合面积更大,受到的负面影响比PNP型晶体管更显著。[22]在一些特殊的应用场合,如核反应堆或航天器中的电子控制系统中,必须采用特殊的手段缓解电离辐射带来的负面效应。

结构

[编辑]

一个双极性晶体管由三个不同的掺杂半导体区域组成,它们分别是发射极区域、基极区域和集电极区域。这些区域在NPN型晶体管中分别是N型、P型和N型半导体,而在PNP型晶体管中则分别是P型、N型和P型半导体。每一个半导体区域都有一个引脚端接出,通常用字母E、B和C来表示发射极(Emitter)、基极(Base)和集电极(Collector)。

基极的物理位置在发射极和集电极之间,它由轻掺杂、高电阻率的材料制成。集电极包围着基极区域,由于集电结反向偏置,电子很难从这里被注入到基极区域,这样就造成共基极电流增益约等于1,而共射极电流增益取得较大的数值。从右边的典型NPN型双极性晶体管的截面简图可以看出,集电结的面积大于发射结。此外,发射极具有相当高的掺杂浓度。[4]:28

在通常情况下,双极性晶体管的几个区域在物理性质、几何尺寸上并不对称。假设连接在电路中的晶体管位于正向放大区,如果此时将晶体管集电极和发射极在电路中的连接互换,将使晶体管离开正向放大区,进入反向工作区。晶体管的内部结构决定了它适合在正向放大区工作,所以反向工作区的共基极电流增益和共射极电流增益比晶体管位于正向放大区时小得多。这种功能上的不对称,根本上是缘于发射极和集电极的掺杂程度不同。因此,在NPN型晶体管中,尽管集电极和发射极都为N型掺杂,但是二者的电学性质和功能完全不能互换。发射极区域的掺杂程度最高,集电极区域次之,基极区域掺杂程度最低。此外,三个区域的物理尺度也有所不同,其中基极区域很薄,并且集电极面积大于发射极面积。由于双极性晶体管具有这样的物质结构,因此可以为集电结提供一个反向偏置,不过这样做的前提是这个反向偏置不能过大,以致于晶体管损坏。对发射极进行重掺杂的目的是为了增加发射极电子注入到基极区域的效率,从而实现尽量高的电流增益。[5]:33-34

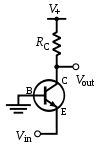

在双极性晶体管的共射极接法里,施加于基极、发射极两端电压的微小变化,都会造成发射极和集电极之间的电流发生显著变化。利用这一性质,可以放大输入的电流或电压。把双极性晶体管的基极当做输入端,集电极当做输出端,可以利用戴维南定理分析这个二端口网络。[23]:90-97利用等效的原理,可以将双极性晶体管看成是电压控制的电流源,也可以将其视为电流控制的电压源。此外,从二端口网络的左边看进去,基极处的输入阻抗减小到基极电阻的,这样就降低了对前一级电路的负载能力的要求。[4]:113

NPN型

[编辑]

NPN型晶体管是两种类型双极性晶体管的其中一种,由两层N型掺杂区域和介于二者之间的一层P型掺杂半导体(基极)组成。输入到基极的微小电流将被放大,产生较大的集电极-发射极电流。当NPN型晶体管基极电压高于发射极电压,并且集电极电压高于基极电压,则晶体管处于正向放大状态。在这一状态中,晶体管集电极和发射极之间存在电流。被放大的电流,是发射极注入到基极区域的电子(在基极区域为少数载流子),在电场的推动下漂移到集电极的结果。由于电子迁移率比空穴迁移率更高,[16]:93因此现在使用的大多数双极性晶体管为NPN型。

双极性晶体管的电学符号如左图,基极和发射极之间的箭头表示发射极电流方向。[24]:64

PNP型

[编辑]双极性晶体管的另一种类型为PNP型,由两层P型掺杂区域和介于二者之间的一层N型掺杂半导体组成。流经基极的微小电流可以在发射极端得到放大。也就是说,当PNP型晶体管的基极电压低于发射极时,集电极电压低于基极,晶体管处于正向放大区。

在双极性晶体管电学符号中,基极和发射极之间的箭头指向电流的方向,这里的电流为电子流动的反方向。与NPN型相反,PNP型晶体管的箭头从发射极指向基极。[24]:102

异质结双极性晶体管

[编辑]

异质结双极性晶体管(heterojunction bipolar transistor)是一种改良的双极性晶体管,它具有高速工作的能力。研究发现,这种晶体管可以处理频率高达几百GHz的超高频信号,因此它适用于射频功率放大、激光驱动等对工作速度要求苛刻的应用。[25][26][27]

异质结是PN结的一种,这种结的两端由不同的半导体材料制成。在这种双极性晶体管中,发射结通常采用异质结结构,即发射极区域采用宽禁带材料,基极区域采用窄禁带材料。常见的异质结用砷化镓(GaAs)制造基极区域,用铝-镓-砷固溶体(AlxGa1-xAs)制造发射极区域。[1]:101采用这样的异质结,双极性晶体管的注入效率可以得到提升,电流增益也可以提高幾个数量级。

采用异质结的双极性晶体管基极区域的掺杂浓度可以大幅提升,这样就可以降低基极电极的电阻,并有利于降低基极区域的宽度。[1]:101在传统的双极性晶体管,即同质结晶体管中,发射极到基极的载流子注入效率主要是由发射极和基极的掺杂比例决定的。在这种情况下,为了得到较高的注入效率,必须对基极区域进行轻掺杂,这样就不可避免地使增大了基极电阻。

如左边的示意图中,代表空穴从基极区域到达发射极区域跨越的势差;而则代表电子从发射极区域到达基极区域跨越的势差。由于发射结具有异质结的结构,可以使,从而提高了发射极的注入效率。在基极区域里,半导体材料的组分分布不均,造成缓变的基极区域禁带宽度,其梯度为以表示。这一缓变禁带宽度,可以为少数载流子提供一个内在电场,使它们加速通过基极区域。这个漂移运动将与扩散运动产生协同作用,减少电子通过基极区域的渡越时间,从而改善双极性晶体管的高频性能。[1]:101-102

尽管有许多不同的半导体可用来构成异质结晶体管,硅-锗异质结晶体管和铝-砷化镓异质结晶体管更常用。制造异质结晶体管的工艺为晶体外延技术,例如金属有机物气相外延(Metalorganic vapour phase epitaxy, MOCVD)和分子束外延。

工作区

[编辑]| 电压 | 发射结偏置 | 集电结偏置 | 工作模式 | |

|---|---|---|---|---|

| NPN型 | ||||

| E < B < C | 正向 | 反向 | 正向 | 放大 |

| E < B > C | 正向 | 正向 | 正向 | 饱和 |

| E > B < C | 反向 | 反向 | 反向 | 截止 |

| E > B > C | 反向 | 正向 | 反向 | 放大 |

| PNP型 | ||||

| E < B < C | 反向 | 正向 | 反向 | 放大 |

| E < B > C | 反向 | 反向 | 反向 | 截止 |

| E > B < C | 正向 | 正向 | 正向 | 饱和 |

| E > B > C | 正向 | 反向 | 正向 | 放大 |

注意:为了清晰地示意物理量,曲线中物理量的比例可能与实际情况有一定差别。

蓝色虚线左边的区域为饱和区(Saturation);由蓝色虚线、红色虚线和棕色虚线包围的区域为放大区(Active),在这个区域里,发射极电流与基极电流成近似线性关系;红色虚线下方表示晶体管尚未导通,处于截止区(Cut-off);为开启晶体管的最小基极电流;图中棕色虚线为晶体管的最大集电极耗散功率,它与两条坐标轴包围的区域为安全工作区,与横轴的交点为最大集电极-基极电压。

可以根据晶体管三个终端的偏置状态,可以定义双极性晶体管几个不同的工作区。在NPN型半导体中(注意:PNP型晶体管和NPN型晶体管的电压描述恰好相反),按发射结(基极-发射极结)、集电结(基极-集电极结)的偏置情况,工作区可以分为为[來源請求]

- 正向放大区(或简称放大区):当发射结正向偏置,集电结反向偏置时,晶体管工作在放大区。大多数双极性晶体管的设计目标,是为了在正向放大区得到最大的共射极电流增益。晶体管工作在这一区域时,集电极-发射极电流与基极电流近似成线性关系。由于电流增益的缘故,当基极电流发生微小的扰动时,集电极-发射极电流将产生较为显著变化。

- 反向放大区:如果把上述处于正向放大区晶体管发射结、集电结的偏置电压互换,则双极性晶体管将工作在反向放大区。在这种工作模式中,发射极和集电极区域扮演的角色与正向放大区里正好相反,但是由于晶体管集电极的掺杂浓度低于发射极,反向放大区产生的效果与正向放大区并不相同。大多数双极性晶体管的设计目标是尽可能得到最大正向放大电流增益,因此,反向放大区中的电流增益会比正向放大区中小一些(在常规的锗晶体管中大约是2-3倍)。实际上,这种工作模式几乎不被采用,但是为了防止错误接法造成器件损坏或其他危险,设计时必须予以考虑。此外,有些类型的双极性逻辑器件也会考虑反向放大区的情况。[28]

- 饱和区:当双极性晶体管中两个PN结均处于正向偏置时,它将处于饱和区,这时,晶体管发射极到集电极的电流达到最大值,即使增加基极电流,输出的电流也不会再增加。饱和区可以在逻辑器件中用来表示高电平。

- 截止区:如果双极性晶体管两个PN结的偏置情况与饱和区恰好相反,那么晶体管将处于截止区。在这种工作模式下,输出电流非常小(小功率的硅晶体管小于1微安,锗晶体管小于几十微安),[4]:33在数字逻辑中可以用来表示低电平。

- 突崩溃:当施加在集电结上的反向偏置将超过集电结所能承受范围时,这个PN结将被击穿,若电流足够大会造成器件损坏。

此外,分析、设计双极性晶体管电路时,还应当注意不能超过双极性晶体管的最大集电极耗散功率。如果晶体管的工作功率小于这一数值,这些工作状态的集合称为安全工作区。如果晶体管的工作功率超过这个限度,将造成器件温度超过正常范围,器件的性能将产生较大的变化,甚至造成损坏。[4]:35硅晶体管允许的结温度介于150摄氏度和200摄氏度之间。可以通过降低内热阻、使用散热片和引入风冷、水冷、油冷等措施来提高最大允许耗散功率。[1]:147

实际上,上述工作区之间并没有绝对的界限,在较小电压变化(小于几百毫伏)范围内,上面提到的不同区域之间可能有一定的重叠。

处于放大区的双极性晶体管

[编辑]

左边这幅示意图,绘出了一个由两个电压源提供偏置的NPN型晶体管,图中箭头代表电流的方向(电子流动的反方向)。为了使晶体管能够在集电极和发射极之间传导较大的电流(大约1毫安的数量级),必须超过某个的最小值,使晶体管被导通,这个最小值常被称为“导通电压”。在室温下,硅双极性晶体管的导通电压通常为650毫伏左右,不过这项参数也随着晶体管的具体类型变化。偏置电压使图中下方的PN结被导通,电子能够从发射极扩散到基极。当晶体管处于放大区,基极和集电极之间的电场(源于)可以使大部分扩散到基极的电子继续通过图中上方的PN结(发射结),以漂移作用进入集电极,这样就形成了集电极电流。剩余的电子与基极区域的多数载流子(即空穴)发生复合,从而形成基极电流。可以看出,发射极电流是流经晶体管的总电流,它是基极、集电极输入电流的总和,即。[4]:31

晶体管工作在放大区时,集电极电流与基极电流的比值被称为直流电流增益。直流电流增益的数值可以随温度变化,不过在有的电路设计中,并不需要依赖其精确值(请参见运算放大器的例子)。直流电流增益以参数表示,而交流信号增益则以表示(参见后面的h参数模型)。如果没有特别考虑在不同频率下的电流增益,即电流变化不太大的时候,常用符号来代表电流增益。[4]:31

另外值得注意的是,发射极电流与成指数关系。在放大器,基极电流与集电极电流近似成线性关系,所以二者的变化趋势相同。[來源請求]

PNP型双极性晶体管的情况与NPN型晶体管类似,不过分析时应注意,其相应的电压值恰好相反。[來源請求]

理论模型

[编辑]下面的将以NPN型双极性晶体管为例进行探讨,PNP型晶体管的原理类似。当NPN型晶体管处于正向放大区时,它的基极-发射极电压、集电极-基极电压均为正值,即发射结为正向偏置,集电结为反向偏置。在放大区内,电子从N型掺杂的发射极区域被注入到P型的基极区域。在基极,电子一方面漂移到到N型掺杂的集电极,一方面与基极区域的多数载流子空穴发生复合。[來源請求]

大信号模型

[编辑]艾伯斯-莫尔模型

[编辑]

1954年,约翰·莫尔(John L. Moll)、朱威尔·艾伯斯(Jewell James Ebers)提出了关于晶体管电流的数学模型。当晶体管处于放大区时,发射极和集电极的直流电流可以利用近似艾伯斯-莫尔模型(简称:EM模型)来描述。假设晶体管为小注入的情况,并且忽略厄利效应,那么艾伯斯-莫尔方程可以表达为[1]:218

基极区域内部的电流主要是由于扩散作用,且

这里

- 为热电压,它的数值等于(在300开尔文时大约为26毫伏)

- 为发射极电流

- 为集电极电流

- 为共基极电流增益,大约在0.98至0.998之间

- 为基极-发射极结上的反向饱和电流(其数量级在10−15到10−12安培之间)

- 为基极-发射极电压

- 为P型区域内的电子扩散常数

- 为基极区域宽度

如果需要研究晶体管在任意工作区时,流经晶体管三个区域的电流,可以利用下面的严格艾伯斯-莫尔方程来求解。下列方程基于双极性晶体管的输运模型。[30]

这里

- 为集电极电流

- 为基极电流

- 为发射极电流

- 为正向共发射极电流增益(介于20到500之间)

- 为反向共发射极电流增益(介于0到20之间)

- 为反向饱和电流(其数量级介于10−15到10−12安培之间)

- 为热电压,在300开尔文时大约为26毫伏

- 为基极-发射极电压

- 为基极-集电极电压

厄利效应

[编辑]在理想的双极性晶体管共射极接法中,如果晶体管工作在放大区,那么集电极电流不随集电极-发射极电压改变,即曲线斜率为0(请参见双极性晶体管的输出特性曲线)。然而,实际情况是,会随着的增加而增加,这种现象是由于厄利效应(或称为基极区域宽度调制效应)。[3]:116根据研究,电流增益也随变化。可以根据下面的公式对上述效应进行计算[31]:317[32]

这里

- 是集电极-发射极电压

- 是热电压,其数值为

- 是厄利电压(介于15伏特到150伏特)

- 是时,双极性晶体管处于共射极接法的电流增益

古梅尔-潘电荷控制模型

[编辑]古梅尔-潘模型是一种详细描述双极性晶体管动力学的电荷控制模型,[33]:827-852借助这个模型,可以比通常的基于终端(terminal-based)模型更为详细地探究晶体管的内部动力原理。[34]该模型还指出,晶体管的参数与流经晶体管的直流电流有关,而该参数在艾伯斯-莫尔模型中曾被认为是与电流无关。[30]:509

古梅尔-潘模型包含的参数相当多,它的直流模型包括多达18个参数,并且参数之间常常具有非线性的关系,因此研究中常常需要借助计算机。[1]:228

小信号模型

[编辑]混合π模型

[编辑]混合模型是小信号情况下对双极性晶体管的线性二端口网络近似,这个模型考虑了晶体管中发射结、集电结的结电容在相对高频情况下的影响,它使用小信号基极-发射极电压和集电极-发射极电压作为自变量,小信号基极电流和集电极电流作为因变量。[31]:13.5, 13.19

右图所示为双极性晶体管的一个基本的低频混合模型示意图,在图中

- ,以欧姆为单位

- 这里

- 为低频电流增益(通常以表示。这里,为静态基极电流。每个晶体管都有对应的,它与集电极电流大小有关。这项参数可以在数据手册中查阅。

- 为厄利效应导致的输出电阻,为厄利效应电压。

h参数模型

[编辑]

在低频小信号的情况里,还可以用参数模型来分析双极性晶体管电路,它也是将晶体管看做一个二端口网络。该模型以输入电流和输出电压为自变量,从而得出等效电路模型。[4]:96利用这种方法,可以较容易地分析双极性晶体管在电路中的行为。在右图中,符号代表不同的晶体管引脚,需要根据晶体管不同的接法来确定。对于共射极接法,

- 被替换为

- 终端1相当于基极

- 终端2相当于集电极

- 终端3相当于发射极

- 为输入的基极电流

- 为输出的集电极电流

- 为输入的基极-发射极电压

- 为输出的集电极-发射极电压

对应的一组h参数为

- 为晶体管的输入阻抗(相当于基极电阻)

- 为晶体管与关系随的变化关系,这项参数的数值通常很小,以至于可以忽略不计。

- 为晶体管的共射极电流增益,即是交流小訊號分析下的交流電流增益,也就是。至於直流分析(大訊號分析)下的則是直流(DC)电流增益(即数据手册中的)。

- 为晶体管的输出阻抗。参数通常相当于双极性晶体管的输出导纳,使用时需要通过对它求倒数转换为阻抗。

参数模型中采用小写字母下标的电学量表示它们为交流的,这意味着模型完全可以用来分析双极性晶体管在较高频率时的性质。对于直流的情况,则采用大写字母来标示这些参数[來源請求]。

参见

[编辑]参考文献

[编辑]- 引用

- ^ 1.00 1.01 1.02 1.03 1.04 1.05 1.06 1.07 1.08 1.09 1.10 1.11 1.12 陈星弼,张庆中. 晶体管原理与设计. 电子工业出版社. 2006. ISBN 7-121-02268-0.

- ^ The Nobel Prize in Physics 1956. Nobelprize.org. [2012-04-09]. (原始内容存档于2014-12-18).

- ^ 3.0 3.1 3.2 孟庆巨,刘海波,孟庆辉. 半导体器件物理. 科学出版社. 2005. ISBN 7-03-013951-8.

- ^ 4.00 4.01 4.02 4.03 4.04 4.05 4.06 4.07 4.08 4.09 4.10 4.11 4.12 4.13 4.14 童诗白,华成英. 模拟电子技术基础(第四版). 高等教育出版社. 2006. ISBN 978-7-04-018922-3.

- ^ 5.0 5.1 5.2 5.3 5.4 5.5 杨凌. 模拟电子线路. 机械工业出版社. 2007. ISBN 978-7-111-22105-0.

- ^ 6.0 6.1 6.2 6.3 6.4 Michael Quirk, Julian Serda. 半导体制造技术(原书名:Semiconductor Manufacturing Technology). 电子工业出版社. 2005. ISBN 7-5053-9493-2.

- ^ 1947 - Invention of the Point-Contact Transistor. Computer History Museum. [2012-04-02]. (原始内容存档于2015-12-21).

- ^ 1948 - Conception of the Junction Transistor. Computer History Museum. [2012-04-02]. (原始内容存档于2012-04-19).

- ^ Third case study–thesolidstateadvent (PDF). The National Archives. [2012-04-07]. (原始内容 (PDF)存档于2007-09-27).

- ^ 10.0 10.1 電晶體的歷史. 羅姆. [2021-03-19]. (原始内容存档于2022-05-18).

- ^ 馮瑞. 固體物理學大辭典. 建宏出版社. : 114 [2016-10-10]. (原始内容存档于2016-10-10) (中文).

鍺的禁帶寬度較窄

- ^ 高文煥 李冬梅. 電子線路基礎(第二版). 北京: 高等教育出版社. 2012: 1. ISBN 978-7-04-016030-7 (中文).

- ^ 李峻霣. 淺談電晶體 (PDF). 台大電機系. [2016-10-10]. (原始内容 (PDF)存档于2016-10-14) (中文).

- ^ 14.0 14.1 周如培,李恩玲,冯同鑫. 现代科学的奇迹-半导体技术. 微电子学. 2001, 31 (2).

- ^ IC Temperature Sensors Find the Hot Spots. MAXIM. 2002-02-21 [2012-04-06]. (原始内容存档于2012-08-05).

- ^ 16.0 16.1 16.2 刘恩科,朱秉升,罗晋生. 半导体物理想(第4版). 国防工业出版社. 2011. ISBN 978-7-118-06562-6.

- ^ 17.0 17.1 R. M. Warner, B. L. Grung. 半导体器件电子学(原书名:Semiconductor-Device Electronics). 电子工业出版社. 2005. ISBN 7-121-00882-3.

- ^ 18.0 18.1 18.2 Paul Horowitz ,Winfield Hill. TheArt of Electronics 2nd. Cambridge University Press. 1989. ISBN 978-0-521-37095-0.

- ^ Juin Jei Liou and Jiann S. Yuan. Semiconductor Device Physics and Simulation. Springer. 1998. ISBN 0-306-45724-5.

- ^ 20.0 20.1 General Electric. Transistor Manual 6th. 1962.

- ^ Paolo Antognetti and Giuseppe Massobrio. Semiconductor Device Modeling with Spice. McGraw–Hill Professional. 1993. ISBN 0-07-134955-3.

- ^ 张华林,陆妩,任迪远,郭旗,余学锋,何承发,艾尔肯,崔帅. 双极晶体管的低剂量率电离辐射效应. 半导体学报. 2004, 25 (12).

- ^ 邱关源. 电路(第5版). 高等教育出版社. 2006. ISBN 978-7-04-019671-9.

- ^ 24.0 24.1 Alphonse J. Sistino. Essentials of electronic circuitry. CRC Press. 1996. ISBN 978-0-8247-9693-8.

- ^ D.V. Morgan, Robin H. Williams (Editors). Physics and Technology of Heterojunction Devices. London: Institution of Electrical Engineers(Peter Peregrinus Ltd.). 1991. ISBN 0-86341-204-1.

- ^ Peter Ashburn. SiGe Heterojunction Bipolar Transistors. New York: Wiley. 2003. Chapter 10 [2012-04-07]. ISBN 0-470-84838-3. (原始内容存档于2009-08-09).

- ^ Bai Dafu, Liu Xunchun, Wang Runmei, Yuan Zhipeng, Sun Haifeng. 高性能新结构InGaP/GaAs异质结双极型晶体管. 半导体学报. 2004, 25 (7).

- ^ 5.3.1. Forward active mode of operation, Principles of Semiconductor Devices. Colorado University. [2012-04-09]. (原始内容存档于2021-04-26).

- ^ Adel S. Sedra and Kenneth C. Smith. Microelectronic Circuits, second ed.. 1987. ISBN 0-03-007328-6.

- ^ 30.0 30.1 A.S. Sedra and K.C. Smith. Microelectronic Circuits 5th. New York: Oxford. 2004. ISBN 0-19-514251-9.

- ^ 31.0 31.1 31.2 R.C. Jaeger and T.N. Blalock. Microelectronic Circuit Design Second Edition. New York: McGraw-Hill. 2004 [2012-04-07]. ISBN 0-07-232099-0. (原始内容存档于2009-02-28).

- ^ Massimo Alioto and Gaetano Palumbo. Model and Design of Bipolar and Mos Current-Mode Logic: CML, ECL and SCL Digital Circuits. Springer. 2005. ISBN 1402028784.

- ^ H. K. Gummel and R. C. Poon. An integral charge control model of bipolar transistors. Bell Syst. Tech. J. May–June 1970, 49.

- ^ 5.6.2. Large signal model (Charge control model), Principles of Semiconductor Devices. Colorado University. [2012-04-07]. (原始内容存档于2009-02-07).

- 書目

-

- 施敏; 伍國珏; 譯者:張鼎張、劉柏村. 半導體元件物理學(上冊). 臺灣: 國立交通大學. 2008-08-01 [2008]. ISBN 978-986-843-951-1 (中文). (繁體中文)

- 施敏; 伍國珏; 譯者:張鼎張、劉柏村. 半導體元件物理學(下冊). 臺灣: 國立交通大學. 2009-04-14 [2009]. ISBN 978-986-843-954-2 (中文). (繁體中文)