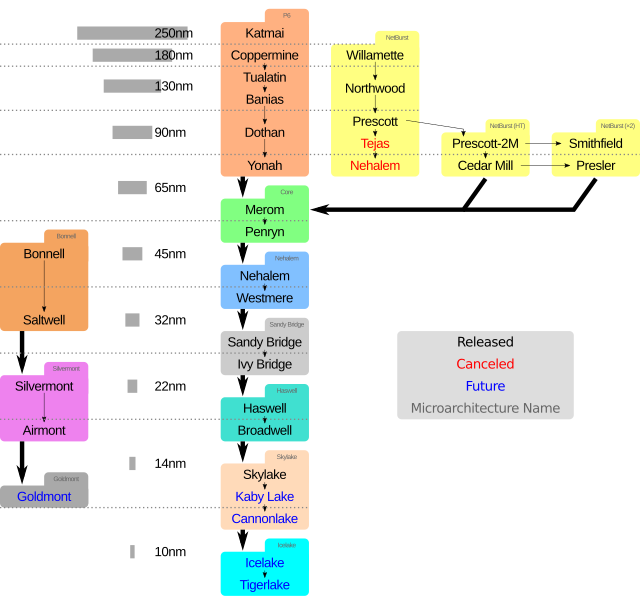

Intel Tick-Tock

Tick-Tock是Intel公司发展微处理器晶片设计制造业务的一种发展战略模式,在2007年正式提出。Intel指出,每一次处理器微架构的更新和每一次晶片制程的更新,它们的时机应该错开,使他们的微处理器晶片设计制造业务更有效率地发展。“Tick-Tock”的名称源于时钟秒针行走时所发出的声响。Intel指,每一次“Tick”代表著一代微架构的处理器晶片制程的更新,意在处理器效能几近相同的情况下,缩小晶片面积、减小能耗和发热量;而每一次“Tock”代表著在上一次“Tick”的晶片制程的基础上,更新微处理器架构,提升效能。一般一次“Tick-Tock”的周期为两年,“Tick”占一年,“Tock”占一年。[1]

此策略常被许多电脑玩家戏称“挤牙膏策略”,因为每一代新处理器效能和前一代处理器效能的差距很短,就好像Haswell的4790K和Skylake的6700K那样。2016年3月22日,Intel在财务报告中宣布放弃Tick-Tock,改用增加优化环节的制程-架构-优化模型。[2]

Intel的主要对手AMD历年来也跟随著Intel的制程脚步做处理器演进,并在2009年于美国分拆出子公司格罗方德作为代工伙伴,一直合作生产直到2018年14奈米的Zen处理器产品为止。由于制程难度提高,AMD在2018年8月底公布消息,取消以格罗方德做为Zen2处理器产品代工伙伴的规划,转用台积电作为代工厂以生产7奈米的Zen2处理器,而此时的Intel之10奈米产线仍因为良率问题无法大规模供货于市场。AMD在2019年11月底宣布,将会继续遵循Intel Tick Tock的精神继续生产Zen2及Zen3处理器。

[3]

环节

[编辑]2016年以前,英特尔仍使用Tick-Tock。

Tick:更新处理器芯片制程。

Tock:更新处理器架构,提升能效比和IPC。

2016年后,Intel已放弃Tick-Tock,改用增加优化环节的制程-架构-优化模型。

目前的环节为:Process, Architecture, Optimization,即制程、架构、优化

制程:在架构不变的情况下,缩小电晶体体积,以减少功耗及成本

架构:在制程不变的情况下,更新处理器架构,以提高性能

优化:在制程及架构不变的情况下,进行修复及优化,将BUG减到最低,并提升处理器时脉

产品发布路线图

[编辑]| 微架构更新 | 微架构 | 制造工艺/制程 | 发布时间 | 处理器 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 八路/四路伺服器平台 处理器核心代号 |

四路/双路伺服器/工作站平台 处理器核心代号 |

极致效能/工作站平台 处理器核心代号 |

主流桌面平台 处理器核心代号 |

流动平台 处理器核心代号 |

处理器品牌 | |||||

| Tick | 制程 | Presler, Cedar Mill, Yonah | 65纳米 | 2006年1月5日 | Presler | Cedar Mill | Yonah | |||

| Tock | 架构 | Core | 2006年6月27日[4] | Kentsfield | Conroe | Merom | ||||

| Tick | 制程 | Penryn | 45纳米 | 2007年11月11日[5] | Dunnington | Harpertown | Yorkfield | Wolfdale | Penryn | |

| Tock | 架构 | Nehalem | 2008年11月17日[6] | Nehalem-EX (Beckton) | Nehalem-EP (Gainestown) | Bloomfield | Lynnfield | Clarksfield | ||

| Tick | 制程 | Westmere | 32纳米 | 2010年1月4日[7][8] | Westmere-EX | Westmere-EP | Gulftown | Clarkdale | Arrandale | |

| Tock | 架构 | Sandy Bridge | 2011年1月9日[9] | — | Sandy Bridge-EP | Sandy Bridge-E | Sandy Bridge | Sandy Bridge-M | ||

| Tick | 制程 | Ivy Bridge | 22纳米 | 2012年4月23日 | Ivy Bridge-EX | Ivy Bridge-EP | Ivy Bridge-E | Ivy Bridge | Ivy Bridge-M | |

| Tock | 架构 | Haswell | 2013年6月4日至6月8日 | Haswell-EX | Haswell-EP | Haswell-WS | Haswell | — | ||

| Process | 制程 | Broadwell[10] | 14纳米[11] | 2014年1月 | Broadwell-EP | Broadwell-E | Broadwell-C | Broadwell-H/Broadwell-U/Broadwell-Y | ||

| Architechture | 架构 | Skylake | 2015年8月5日 | Skylake-S | Skylake-H/Skylake-U/Skylake-Y | |||||

| Optimization | 优化 | Kaby Lake | 14奈米+ | 2016年8月30日 | Kaby Lake-S | Kaby Lake-H/Kaby Lake-U/Kaby Lake-Y | ||||

| Optimization | 优化 | Coffee Lake | 14奈米++ | 2017年10月5日 | Coffee Lake-S | |||||

| Process | 制程 | Cannon Lake | 10纳米 | 2018年 | ||||||

| Architechture | 架构 | Ice Lake | 2019年 | |||||||

| Optimization | 优化 | Tiger Lake | 2020年 | |||||||

| Optimization | 优化 | 10奈米++ | 20xx年 | |||||||

| Process | 制程 | 7纳米 | 20xx年 | |||||||

| Architechture | 架构 | 20xx年 | ||||||||

| Optimization | 优化 | 20xx年 | ||||||||

| Optimization | 优化 | 7奈米++ | 20xx年 | |||||||

参见

[编辑]参考资料

[编辑]- ^ Intel Tick-Tock Model. [2012-06-06]. (原始内容存档于2017-01-07).

- ^ Cutress, Ian. Intel’s ‘Tick-Tock’ Seemingly Dead, Becomes ‘Process-Architecture-Optimization’. www.anandtech.com. [2022-07-25]. (原始内容存档于2020-11-27).

- ^ 存档副本. [2019-12-18]. (原始内容存档于2019-12-18).

- ^ Intel CEO: Latest Platforms, Processors Form New Foundations For Digital Entertainment And Wireless Computing (页面存档备份,存于互联网档案馆), Intel Unveils World's Best Processor (页面存档备份,存于互联网档案馆)

- ^ Intel Unveils 16 Next-Generation Processors, Including First Notebook Chips Built on 45nm Technology. [2012-06-06]. (原始内容存档于2009-02-18).

- ^ Intel Launches Fastest Processor on the Planet. [2012-06-06]. (原始内容存档于2011-12-21).

- ^ 存档副本 (PDF). [2012-06-06]. (原始内容存档 (PDF)于2012-10-02).

- ^ Revolutionizing How We Use Technology—Today and Beyond. [2012-06-06]. (原始内容存档于2011-06-05).

- ^ Intel Sandy Bridge chip coming January 5. [2012-06-06]. (原始内容存档于2012-05-16).

- ^ 引用错误:没有为名为

BroadwellSA的参考文献提供内容 - ^ 存档副本 (PDF). [2012-06-06]. (原始内容存档 (PDF)于2013-07-06).