單片系統

此條目可參照英語維基百科相應條目來擴充。 |

單片系統或片上系統(英語:System on a Chip,縮寫:SoC)是一個將電腦或其他電子系統集成到單一芯片的集成電路[1]。單片系統可以處理數字信號、模擬信號、混合信號甚至更高頻率的信號。單片系統常常應用在嵌入式系統中[2]。單片系統的集成規模很大,一般達到幾百萬門到幾千萬門。[3]

儘管微控制器通常只有不到100kB的隨機存取存儲器,但是事實上它也是一台小電腦的結構,一種簡易的、功能弱化的單芯片系統,而一般認知的「單片系統」這個術語常被用來指功能更加強大的處理器,這些處理器可以運行Windows和Linux的某些版本。單片系統更強的功能要求它具備外部存儲芯片,例如有的單片系統配備了閃存。單片系統往往可以連接額外的外部設備。單片系統對半導體器件的集成規模提出了更高的要求。為了更好地執行更複雜的任務,一些單片系統採用了多個處理器核心。[4]:1

基本架構

[編輯]

典型的單片系統具有以下部分:

- 至少一個微控制器或微處理器、數字信號處理器,但是也可以有多個中央控制核心

- 記憶體則可以是唯讀記憶體、隨機存取存儲器、EEPROM和閃存中的一種或多種

- 用於提供時間脈衝信號的振盪器和鎖相環電路

- 由計數器和計時器、電源電路組成的外部設備

- 不同標準的連線接口,如通用串行總線、火線、以太網、通用異步收發和序列周邊介面等

- 用於在數字信號和模擬信號之間轉換的模擬數字轉換器和數字模擬轉換器

- 電壓調理電路以及穩壓器

數據的流動主要藉助了系統中的I/O總線,例如安謀國際科技公司的高級微控制器總線架構。採用DMA控制器,則可以使得外部數據直接被傳送到存儲器,無需經過中央處理器,這可以大大改善數據吞吐的效率。

設計流程

[編輯]

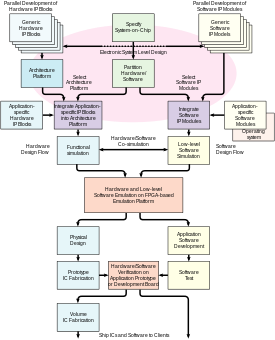

一個完整單片系統由硬件和軟件兩部分組成,其中軟件用於控制硬件部分的控制器、微處理器或數字信號處理器核心以及外部設備和接口。單片系統的設計流程主要是其硬件和軟件的設計。

由於單片系統的集成度已經達到數百萬門,工程師必須儘可能採取可重用的設計思路。大部分的單片系統都使用了預定義的半導體知識產權核(IP核,包括軟核、硬核和固核),以可重用設計的方式來完成快速設計。與以往的集成電路設計相比,可重用設計要求設計人員的工作更加標準化,例如規範的代碼書寫風格等等。[4]:4-5[4]:68-110設計人員需要關注硬件驅動程序的實現,從而實現具體的功能。協議棧是一個重要的概念,它與諸如通用串行總線的接口的工業標準有關。設計人員通常使用計算機輔助工程工具來把已經設計(或者購買)的核連接在一起,這時集成開發環境可以被用來整合包含不同子功能的模塊。

設計的芯片在被送到工廠進行硬件工藝製造之前,設計人員會採取不同方式對芯片的邏輯功能進行驗證。功能驗證的重要性絲毫不亞於集成電路設計,對於現代的超大規模集成電路,這一步驟在整個設計周期中將花費相當的時間和金錢。[5]為了應對芯片極高的複雜程度,類似SystemVerilog、SystemC、e驗證語言和OpenVera的硬件驗證語言逐漸變得流行。在驗證階段,系統軟件的程序錯誤可以被反饋到設計人員那裡,以便進行針對性的修正。

工程師通常會使用精心設計的仿真器或者在通用的現場可編程邏輯門陣列(FPGA)上運行程序,來測試之前進行的系統級、行為級(或用另一個術語寄存器傳輸級,即RTL)的設計代碼,這一步的目的是在設計項目在進行最後的硬件生產(投片)之前,其軟、硬件的功能、性能得到最後的確認,並改正所有功能、時序、功耗上的錯誤。

其中,使用現場可編程邏輯門陣列構建產品原型的工作方式可以讓工程師評估、測試各種刺激(stimulus)施加在系統時,系統的運行狀態。相關的電子設計自動化工具包括Certus[6],它可以被用來分析、檢測系統設計的寄存器傳輸級代碼,監視其中的變量和信號在整個運行過程中的變化。

在功能驗證過程結束之後,工程師還會採取計算機輔助工程的方式完成布局、布線流程,這一步他們需要關注何種布局布線方式可以儘可能地減少連線之間的信號干擾和延遲,功率也是另外一個考慮的重點。[4]:42-46

參考文獻

[編輯]- ^ Atlantic. Encyclopedia Of Information Technology. Atlantic Publishers & Dist. 13 June 2007: 461– [30 January 2013]. ISBN 978-81-269-0752-6.

- ^ Ian Grout. Integrated Circuit Test Engineering: Modern Techniques. Springer. 2006: 225– [30 January 2013]. ISBN 978-1-84628-173-0.

- ^ 虞希清. 专用集成电路设计实用教程. 浙江大學出版社. : 3. ISBN 978-7-308-05113-2.

- ^ 4.0 4.1 4.2 4.3 Michael Keating, Pierre Breacaud. 片上系统——可重用设计方法学(第二版)(英文名:Reuse Methodology Manual for System-on-a-Chip Designs, Third Edition). 北京: 電子工業出版社. 2004. ISBN 7-5053-9338-3.

- ^ Is verification really 70 percent?. Eetimes.com. [2009-08-12].[永久失效連結]

- ^ Tektronix hopes to shake up ASIC prototyping. EE Times. 2012-10-30 [2012-10-30].[永久失效連結]

相關條目

[編輯]