可程式化邏輯裝置

可程式化邏輯裝置(英語:Programmable Logic Device,縮寫為PLD)是一種電子零件、電子組件,簡而言之也是一種集成電路、晶片。PLD晶片屬於數碼型態的電路晶片,而非模擬或混訊(同時具有數碼電路與模擬電路)晶片。

PLD與一般數碼晶片不同的是:PLD內部的數碼電路可以在出廠後才規劃決定,有些類型的PLD也允許在規劃決定後再次進行變更、改變,而一般數碼晶片在出廠前就已經決定其內部電路,無法在出廠後再次改變,事實上與一般的模擬晶片、混訊晶片一樣,在出廠後就無法再對其內部電路進行調修。

發明之前

[編輯]

在PLD還未被發明前,已有人將唯讀記憶體(ROM)晶片以PLD的概念來運用,用ROM晶片來充當一些輸入性的組合邏輯(combinatorial logic)函數。

首先一顆ROM晶片有m個輸入(地址線,或稱:地址匯流排、定址線)以及n個輸出(資料線,也稱:資料匯流排,在此也可稱:資料輸出線),當ROM被當成記憶體使用時,它就有個n bits的記憶儲存空間。

輸入部分不再是個m-bit的地址線路,而被看成是有m個相互無關連的獨立邏輯訊號線。且就理論而言一顆ROM晶片內可以放置個布林(Boolean)函數,且每個布林函數可以有m個邏輯訊號。

但是這種用ROM「喬裝」成的PLD,礙於ROM自身原有的結構設計,使真正有效的函數數取決於輸出接腳(也稱:腳位、引腳)數,因此有n個輸出就只能有n個可用的有效函數。更簡單的說,這時候的ROM等同於n組相互無關的獨立邏輯電路,每組電路的產生、形成,則取決於由m個輸入所組成的邏輯函數。

使用ROM來當PLD的好處是:有幾個以m輸入方式表示的邏輯函數,就會有幾個對應的n輸出,且絕大多數一般性用途的組合邏輯裝置都可適用此種作法。同樣的,PROM(Programmable ROM)、EPROM(ultraviolet-Erasable PROM)、EEPROM(Electrically Erasable PROM)等也都可以用此種方式進行邏輯規劃、程式化,而且不需要特殊的軟硬件,只要用標準的PROM燒錄器即可實現程式化。然而,無論怎麼說,這種作法也有些缺點:

- 與真正專精的邏輯電路相比,在反應速度表現上慢了太多。

- 在非同步(也稱:非同步)的邏輯狀態轉變下,無法提供安全性的狀態「防護,cover」。

- 過於耗電(同樣是與真正專精的邏輯電路相比)。

- 整個ROM中僅有小部分的記憶儲存空間能被有效使用,其餘都形同浪費。

此法也不易於用於序向邏輯電路(sequential logic)中,因為ROM裏頭並不具備正反器(flip-flop,簡稱:FF)。

對電路設計的業餘愛好者來說,有時也仍然用普遍型EPROM晶片來充當PLD,這種用法有時也稱為「窮人的PAL」(PAL是PLD的一種)。

早期的可程式邏輯

[編輯]

第一個在商業化市場運用的PLD,是由Monolithic記憶體公司(Monolithic Memories, Inc.,簡稱:MMI)所推出的可程式化陣列邏輯(Programmable Array Logic,簡稱PAL)(此點有爭議,詳見討論頁),雖然IBM公司在1970年代中也有研製類似的裝置(元件),但僅在該公司內部使用。

MMI公司在20-pin(20支接腳、引腳、腳位)的PAL方面相當成功,之後超微(AMD)公司也推出了22V10,22V10也是顆PAL,具有原先PAL所有的特性特點,但接腳數增至24-pin。更之後AMD公司收併了MMI公司(約1987年,待查證),並將其納入自身的PLD部門,數年後AMD以百分之百轉投資的方式將PLD部門分立成獨立的威特信(Vantis)公司,到了1999年則由萊迪思半導體公司收購AMD公司手中的Vantis公司股份,自此收併Vantis公司。

GAL

[編輯]以PAL(可程式陣列邏輯)為基礎的接續創新是通用陣列邏輯(Generic Array Logic, GAL),此是由萊迪思半導體公司所發明,GAL的特性與PAL相同,不過PAL的電路組態、組態只能進行一次的程式燒錄,不能再有第二次,而GAL則是可以反覆對電路組態、組態進行燒錄、清除、再燒錄、再清除。

GAL這種可重複燒錄的特性在研發過程時的試製階段(prototyping stage)中特別好用,一旦在邏輯電路的設計上發現有任何程式錯誤,若是用GAL就能夠以重新燒錄的方式來修正錯誤。此外GAL也可以用PAL的燒錄器來進行燒錄及再燒錄,雖然現在已經有可線上燒錄(In-Circuit Programmable,有時也稱:In-System Programmable)的ispGAL22V10。

另一個與GAL相類似的是PEEL(Programmable Electrically Erasable Logic),是由International CMOS Technology(簡稱:ICT)公司所提出。

CPLD

[編輯]

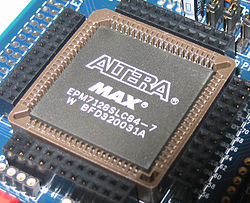

PAL、GAL僅適合用在約數百個邏輯門所構成的小型電路,若要實現更大的電路則適合用CPLD(Complex PLD,複雜型PLD),一顆CPLD內等於包含了數顆的PAL,各PAL(邏輯區塊)間的互接連線也可以進行程式性的規劃、燒錄,CPLD運用這種多合一(All-In-One)的整合作法,使其一顆就能實現數千個邏輯門,甚至數十萬個邏輯門才能構成的電路。

至於CPLD的程式燒錄方式,雖然有些CPLD可以用PAL的燒錄器來進行燒錄,但這種燒錄方式對經常有數百隻接腳的CPLD來說並不方便。另一種燒錄方式是CPLD已焊於印刷電路板上,之後透過額外的臨時外接,或原有線路的內接,使CPLD與個人電腦間能取得連線,由個人電腦以串列或並列方式將新的燒錄資料傳送到CPLD上,而CPLD內部也具有解碼電路能對接收到的資料進行還原解析,之後再進行重新的燒錄,以此方式讓CPLD內的程式(也可稱:電路)獲得更新。

要注意的是,每家業者的CPLD晶片多具有焊接後再行傳輸、再次燒錄的技術,但各家的技術實現方式與名稱多不盡相同,例如萊迪思半導體公司就將此種燒錄技術稱為「in-system programming」。

各家獨創、專屬的作法也逐漸消失,朝共通的標準、一致的方向發展,如IEEE 1532。

FPGA

[編輯]

當PAL忙於進展成GAL、CPLD時,另一種「可程式化」的流派也逐漸成形,此稱之為場式可程式閘陣列(Field Programmable Gate Array,簡稱:FPGA)或現場可程式閘陣列,FPGA是以閘陣列(Gate Array)技術為基礎所發展成的一種PLD。

FPGA早期的例子是Signetics公司在1970年代晚期所推出的82S100(陣列)及82S105(定序器、編序器),其中82S100為「與,AND」型的閘陣列,而82S105也相同,但再追加正反器(Flip Flop,cn處也稱:觸發器)的功能。

FPGA運用一種邏輯門式的網格(Grid),這種網格與普通的「閘陣列」相類似,網格可以在FPGA晶片出廠後才進行組態組態的程式性規劃。至於為何要稱「場式可程式化」就有些難懂了,「場式,Field」對晶片生產廠以外的世界來說是個工程方面的專業術語,然而廠外也是晶片買主的所在處。(言下之意是:不應當以這種艱澀難懂的工程用詞來做為晶片產品的推行名稱)

FPGA通常也可以在焊接後再進行程式燒錄、變更的工作,此在某種程度與大型的CPLD相似。而絕大多數的FPGA,其內部的程式組態組態是屬於揮發性的,即是無持續電力供應後組態組態的內容就會消失,所以在裝置(也指:元件、晶片)重新獲得電力後,就必須將組態組態內容重新載入(re-load)到FPGA中,或者期望改變FPGA內的組態組態時,也必須進行重新載入的動作。

而關於組態組態的內容,就一般來說會存放在非揮發性的記憶體中,如PROM或EEPROM,若是用EEPROM,則或許也能用線上燒錄(In-System Programmable,ISP)的方式來再次改變組態組態的內容(一般來說是透過JTAG介面來進行ISP)。

FPGA與CPLD都很適合用在特殊、特定的工作上,這是以此類晶片的技術本質來做為合適性的考量,然而有時在以經濟性為主的權衡評估下也適合使用FPGA、CPLD,或者有時也會以工程師的個人偏好與經驗來決定。

其他型態的PLD

[編輯]除上述外,也有許多可再組態組態的系統(多指「晶片」)。例如:有些微處理器內除了一些固定性功效的電路外,其他部分的電路則可以依據微處理器所執行的程式碼而改變其功效。要想設計這種半變動式的系統,工程師需要學習新方法,甚至可能要用新的軟件工具才能夠開發。

另外,現在銷售的PLD中,有的也會在晶片內提供一個具固定性功效的微處理器,然後微處理器的四周位置則設有許多可供組態組態的可程式邏輯(也因為處理器位在其中,所以也被稱為核心),此種作法的好處是可以讓設計者更專注在為他的設計增加新的功能特點,而少去擔心「如何讓微處理器運作」之類的基礎性設計。

維持PLD的電路組態與組態

[編輯]在一個PLD內有邏輯部分也有記憶部分,記憶部分是用來儲存組態組態的程式內容,而儲存的方式多是存放在可供PLD使用的集成電路(也稱:集成電路)中,這包括:

- Silicon antifuses(矽反熔絲)

- SRAM(靜態隨機存取記憶體)

- EPROM or EEPROM cells(EPROM或EEPROM的記憶晶格)

- Flash memory(快閃記憶體,也稱:閃存)

矽反熔絲主要是用於PAL內,方式上是在PAL內部可程式化的矩陣中,若期望矩陣中的某處、某一位置能夠形成連接連線,則對該位置的行、列兩端施壓一個燒錄燒寫電壓(此電壓通常高於一般運作時的電壓),如此該位置就會形成連接的短路、閉路(short)狀態,相反的未施加電壓的地方則保持開路(open)狀態,由這開路、閉路來形成邏輯的0、1儲存。不過一旦某位置被施加燒寫電壓而形成短路後,就無法在恢復成開路狀態,但其他仍保持開路的位置,仍可施壓電壓使其短路,不過整體來說矽反熔絲僅適合一次性的組態組態燒錄,一旦燒寫的內容有錯誤,該顆PAL即宣佈報廢。此外,之所以稱為「反熔絲」,理由是它的特性原理恰巧與一般日常所用的熔絲、保險絲相反,保險絲平時為短路,而被施加較高電壓時便會燒斷,成為永久性的斷路、開路,反熔絲卻是平常為斷開,施加電壓後反成為連接的短路、閉路。

SRAM屬於揮發性的記憶體,這表示它在每次失去供電後就無法儲存資料,若有PLD使用SRAM做為其組態組態的儲存記憶(多數為FPGA),則每一次重新供電後就必須再次將組態組態資料載入(load,用意等同於將程式燒錄燒寫到PLD內)到PLD的SRAM中,不過此一送電後重新載入的程式,通常是交由另一部份的電路以自動化方式來執行,此一「開機後自動將程式載入到PLD內」的電路,過去是在PLD外部另行設計,但現在也有整合(也稱:整合)到PLD內部的作法。

EPROM的記憶晶格是一種MOS(metal-oxide-semiconductor,金屬氧化半導體)型的電晶體,若對該電晶體的閘極進行充電,則該充電後的狀態就會成為一個記憶留存,之後無論晶片有無供電都可以持續維持着該狀態,直到數年後充電狀態才會消退消失,而透過對各記憶晶格的充電有無就能夠儲存0、1的組態組態。至於記憶資料當如何抹除(也稱:拭除、擦除),這必須用強烈的紫外線對EPROM進行照射,以此強迫各閘極將原有的充電加以釋放,且時間必須長達數十分鐘才能全部抹除,否則會有抹除不完整的情形,此一抹除程式多是用所謂的「紫外線EPROM抹除盒」,英文稱EPROM eraser,即是一個小盒子內設有紫外線燈管,之後將EPROM放入盒內,再將盒子的電源開啟並點亮紫外線燈管,讓紫外線照射EPROM,以此來進行清除,也因為紫外線對人體有害,所以才要在密閉不透光的小盒子內進行照射,此外為了方便工程師使用,抹除盒通常還設有定時裝置,時間到後會自動提醒工程師已經達當初設置的照射時間。

快閃記憶體具有非揮發性,即是斷電後仍可儲存記憶內容,且需要時它也隨時能再清除抹除(erase)、再燒錄燒寫(program、reprogram)。

時至2005年,多數的CPLD都已使用電氣方式燒寫與電氣方式抹除,並以非揮發性方式來記憶。因為經過事實驗證,在太小的邏輯運用中用SRAM來儲存邏輯組態組態,則每次重新送電啟動就必須再次進行載入燒寫,如此實在過於麻煩,所以才會改成以非揮發方式來進行記憶儲存。此外,若是用EPROM方式進行儲存,且為了能夠再次抹除與再次燒寫,則PLD在其晶片封裝上就必須使用陶瓷材質的封裝,並在EPROM裸晶(Die)位置的上端設立石英材質的透光窗,好讓紫外線能夠照射入內,如此才能抹除EPROM裸晶上所儲存的組態組態資料,而這種封裝方式遠貴於一般的塑膠材質封裝。

PLD的程式語言

[編輯]以手工的方式來產生JEDEC檔過於複雜,所以多半改用電腦程式來產生,這種程式稱為「邏輯編譯器」(logic compiler),它與程式開發撰寫時所用的軟件編譯器相類似,而要編譯之前的原始程式碼也得用特定的程式語言來撰寫,此稱之為硬件描述語言(hardware description language, HDL)。

硬件描述語言並非僅有一種,如ABEL、AHDL、Confluence、CUPL、HDCaml、JHDL、Lava、Lola、MyHDL、PALASM、RHDL等,但目前最具知名也最普遍使用的是VHDL與Verilog HDL。

附註

[編輯]- ^ - 就理論發展過程而言,在ROM類還歷經了一小段PLA(Programmable Loigic Array)發展,之後才有PAL,ROM、PLA三者的主要差別是:ROM僅在輸出的OR(或)陣列可進行組態組態的規劃,而PAL僅能在輸入的AND(與)陣列進行規劃,而PLA兩者皆可。

- ^ - 事實上除了可覆寫(Rewritable)外,GAL與PAL間的更大差別在於GAL的輸出端追加了輸出巨集晶格(Ouput Logic Macrocell,簡稱:OLMC)的設計,使邏輯輸出有更多的控制方式,使GAL比PAL更方便用在與序向邏輯電路的搭配上。(「巨集」也稱為「宏」)

- ^ - 相對於「Field-Programmable,場燒錄」一詞的是「Mask-Programmable,遮罩、遮蓋式刻錄」,即是指用光罩(Mask,也稱:掩膜)方式曝光後蝕刻而成的電路,也就是ASIC的製程方式,只能在晶圓廠使用的程式燒錄法,更正確的說是:(積體、整合)電路的製造法。