抗辐射强化

此条目翻译品质不佳。 (2024年6月1日) |

抗辐射强化是使电子元件和电路能够抵抗高幅度游离辐射(粒子辐射和高能电磁辐射)造成的损坏或故障的过程, [1]特别适用于外太空(特别是在低地球轨道以外)、核反应堆和粒子加速器周围,或在核事故或核战期间的环境。

大多数半导体电子元件都易受辐射损伤,而抗辐射( rad-hard )元件是基于非抗辐射元件而制造的,并进行了一些设计和制造上的改进,以降低受辐射损伤的敏感性。由于生产耐辐射微电子芯片设计需要大量的开发和测试,抗辐射芯片的技术往往落后于最新的发展。

抗辐射产品通常要经过一项或多项结果效应测试,包括总电离剂量 (TID)、增强型低剂量率效应 (ELDRS)、中子和质子位移损伤以及单粒子效应 (SEE)。

辐射引起的问题

[编辑]高浓度游离辐射的环境对电子设备的设计带来了特殊挑战。一个带电粒子可以撞击与激发数千个电子,造成电子噪声和讯号突波。对于数位电路来说,这可能会导致数据错误或无法解析的讯号,影响系统的正常运行。这在卫星、太空飞行器、未来量子电脑、 [2] [3] [4]军用飞机、核电站和核武器的设计中是一个特别严重的问题。

为了确保此类系统正常运行,针对军事或航空太空市场的集成电路和传感器制造商采用了各种抗辐射技术。由此产生的系统被称为抗辐射 ( rad(iation)-hardened )、辐射硬化 (rad-hard) 或辐射固化的 (hardened) 系统。

主要辐射损伤源

[编辑]电子设备受到游离辐射的典型来源是:人造卫星的范艾伦辐射带、发电厂传感器和控制电路的核反应堆、控制电子设备(尤其是粒子探测器设备)的粒子加速器、芯片封装材料中同位素的残留辐射、太空船和高空飞机的宇宙辐射、以及所有军用和民用电子设备受到核爆所带来的辐射。

- 宇宙射线来自四面八方,由大约 85% 的质子、14% 的α粒子和 1% 的重离子以及X 射线和伽马射线组成。大多数效应是由能量在 0.1 至 20 GeV之间的粒子引起的。这些大部分会被大气层过滤掉,因此它们主要对太空船和高空飞机造成影响,但也会有机会影响地面上的普通电脑。 [5] [6]

- 太阳粒子事件来自太阳方向,由大量高能(几 GeV )质子和重离子流组成,同样伴随着 X 射线。

- 范艾伦辐射带包含被地磁场捕获的电子(高达约 10 MeV)和质子(高达 100s MeV)。距离地球较远区域的粒子通量可能根据太阳和磁层的实际情况而发生很大变化。在这个位置主要会对人造卫星构成威胁。

- 核反应堆产生伽马辐射和中子辐射,会影响核电站的传感器和控制电路。

- 次级粒子则由这边所述的各种辐射与电子设备周围结构交互作用而产生。

- 粒子加速器产生高能质子和电子,它们相互作用产生的次级粒子会对敏感的控制和粒子探测器部件产生严重的辐射损伤,对于大型强子对撞机等系统来说,其数量级为 10 MRad[Si]/年。 [7]

- 核爆透过频率宽广的电磁辐射、电磁脉冲(EMP)、中子辐射以及初级和次级带电粒子流产生短暂而极其强烈的涌浪电流。一旦爆发核战争,它们将对所有民用和军用电子设备构成潜在威胁。

- 芯片封装材料是一种危险的辐射源,1970 年代发现它会导致新型DRAM芯片出现软性错误。芯片封装中的微量放射性元素会产生α粒子,偶尔会对一些用于存储 DRAM 数据位的电容器放电。如今,通过使用纯度更高的封装材料以及采用纠错码来检查并纠正 DRAM 错误,其影响已经大大减轻。

辐射对电子产品的影响

[编辑]基本机制

[编辑]有两种基本的损坏机制:晶格位移和电离效应。

晶格位移

[编辑]晶格位移是由中子、质子、α粒子、重离子和极高能伽马光子引起的。它们改变晶格中原子的排列,造成持久损伤,增加复合中心的数量,耗尽少数载流子,并使受影响的半导体P-N结的模拟特性恶化。与直觉相反的是,短时间内较高的剂量会导致受损晶格的部分退火(“修复”),导致的损伤程度低于长时间以低强度输送的相同剂量(LDR 或低剂量率)。这类问题在双极晶体管中尤为明显,因为双极晶体管依赖于基极的少数载流子;复合引起的损耗增加会导致晶体管增益损失(参见中子效应)。经认证为不含 ELDRS(增强型低剂量率敏感)的组件,在通量低于 0.01 rad(Si)/s = 36 rad(Si)/h 时不会出现损坏。

电离效应

[编辑]电离效应是由带电粒子引起的,包括能量太低而无法引起晶格效应的粒子。电离效应通常是瞬态的,会产生故障和软错误,但如果它们触发其他损坏机制(例如闩锁),则可能导致设备损坏。紫外线和X射线辐射引起的光电流也可能属于这一类。 MOSFET晶体管氧化层中空穴的逐渐积累会导致其性能下降,当剂量足够高时,甚至会导致元件故障(参见总电离剂量效应)。

由于所有参数的不同,其影响可能会有很大差异——辐射类型、总剂量和辐射通量、辐射类型的组合,甚至设备负载类型(工作频率、工作电压、晶体管被粒子撞击瞬间的实际状态)——这使得彻底的测试变得困难、耗时,并且需要大量的测试样本。

产生的效果

[编辑]“最终用户”的影响可以分为几类,

与半导体晶格相互作用的中子将取代其原子。这导致复合中心和深能级缺陷的数量增加,从而缩短少数载流子的寿命,从而对双极元件的影响比CMOS元件更大。硅基双极元件的电参数在10 10至10 11中子/cm 2水平时就会发生变化,而CMOS元件在10 15中子/cm 2以上时才会受到影响。随着积体度的提高和单个结构尺寸的减小,设备的灵敏度可能会同时提高。中子活化还存在引起感生放射性的风险,中子活化是高能天体物理仪器的主要噪声源。感应辐射和所用材料中的杂质产生的残留辐射可能会在设备的使用寿命内引发各种单粒子问题。光耦合器中常见的GaAs LED对中子非常敏感。晶格损伤对晶体振荡器的频率产生影响。带电粒子的动能效应(即晶格位移)也属于此类。

总电离剂量效应

[编辑]游离辐射在暴露时间内对半导体晶格造成的累积损伤(晶格位移损伤)。它以拉德为单位进行测量,会导致设备性能缓慢逐渐下降。在几秒到几分钟内输送到硅基设备的总剂量超过 5000 拉德将导致长期性能下降。在CMOS元件中,辐射会在栅极绝缘层中产生电子-空穴对,它们在复合过程中会产生光电流,而绝缘体中晶格缺陷中捕获的空穴会产生持续的栅极偏置并影响晶体管的阈值电压,使N型MOSFET晶体管更容易导通,而P型晶体管更难导通。累积的电荷可能足够高,使晶体管永久打开(或关闭),从而导致设备故障。随着时间的推移,一些自我修复会发生,但这种效果并不是太显著。这种效应与高积体度高速电子元件中的热载流子退化相同。晶体振荡器对辐射剂量有一定的敏感度,辐射剂量会改变其频率。使用扫频石英可以大大降低灵敏度。天然石英晶体特别敏感。可以为所有结果效应测试程序生成 TID 测试的辐射性能曲线。这些曲线显示了整个 TID 测试过程中的性能趋势,并包含在辐射测试报告中。

瞬时剂量效应

[编辑]短时高强度辐射脉冲,通常发生在核爆炸期间。高辐射通量在整个半导体中产生光电流,导致晶体管随机打开,从而改变触发器和存储单元的逻辑状态。如果脉冲持续时间太长,或者脉冲导致结损坏或闩锁,则可能会造成永久性损坏。闩锁通常是由核爆炸的 X 射线和伽马辐射闪光引起的。由于石英中诱发的瞬时光电导,晶体振荡器可能会在闪光持续期间停止振荡。

系统产生的电磁脉冲效应

[编辑]SGEMP 是由辐射闪光穿过设备并在芯片、电路板、电缆和外壳的材料中引起局部电离和电流引起的。

数位损坏:SEE

[编辑]自 20 世纪 70 年代以来,单事件效应(SEE)得到了广泛的研究。 [8]当高能粒子穿过半导体时,它会留下电离轨迹。这种电离可能引起与瞬态剂量类似的高度局部效应 - 输出中的良性故障,存储器或寄存器中的不太良性的位翻转,或者特别是在高功率晶体管中的破坏性的闩锁和烧毁。单粒子效应对于卫星、飞机和其他民用和军用航空航太应用中的电子设备具有重要意义。有时,在不涉及闩锁的电路中,引入RC时间常数电路会有所帮助,这会使电路的反应时间减慢至 SEE 持续时间以外。

单粒子瞬态

[编辑]当从电离事件中收集的电荷以杂散讯号的形式在电路中传播时,就会发生 SET。这实际上是静电放电的效应。软错误,可逆。

单事件颠覆

[编辑]电子产品中的单粒子翻转(SEU) 或瞬态辐射效应是由单个离子与芯片相互作用引起的存储器或寄存器位的状态变化。它们不会对设备造成持久损坏,但可能会对无法从此类错误中恢复的系统造成持久问题。软错误,可逆。在非常敏感的设备中,单个离子可能会导致几个相邻的存储单元出现多位翻转(MBU)。当 SEU 扰乱控制电路(如状态机)时,它们会变成单事件功能中断( SEFI ),使设备进入未定义状态、测试模式或停止状态,然后需要重置或电源循环才能恢复。

单粒子闩锁

[编辑]SEL 可以出现在任何具有寄生 PNPN结构的芯片中。重离子或高能质子穿过两个内部晶体管结之一,可以开启类似晶闸管的结构,然后该结构保持“短路”状态(这种效应称为闩锁),直到设备重新通电。由于这种影响可能发生在电源和基板之间,因此可能会产生破坏性的高电流,导致部件失效。硬错误,不可逆。体硅 CMOS 元件最容易受到影响。

单粒子回跳类似于 SEL,但不需要 PNPN 结构,可以在切换大电流的 N 沟道 MOS 晶体管中感应产生,当离子撞击漏极结附近并导致电荷载流子的雪崩倍增时。然后晶体管打开并保持打开状态,这是一个不可逆的硬错误。

单一事件引发的倦怠

[编辑]当源区正下方的衬底正向偏置且漏源电压高于寄生结构的击穿电压时,功率 MOSFET 中可能会出现 SEB。由此产生的高电流和局部过热可能会损坏设备。硬错误,不可逆。

单事件门破裂

[编辑]当重离子撞击栅极区域且在栅极施加高电压时,在功率 MOSFET 中观察到 SEGR。然后,二氧化硅绝缘层就会发生局部击穿,导致栅极区域局部过热和破坏(看起来像微观爆炸)。即使在EEPROM单元中写入或擦除时,当单元受到相对较高的电压时,也会发生这种情况。硬错误,不可逆。

SEE 测试

[编辑]尽管质子束因其可用性而被广泛用于 SEE 测试,但在较低能量下,质子辐照通常会低估 SEE 敏感性。此外,质子束使设备面临总电离剂量 (TID) 故障的风险,这可能会影响质子测试结果或导致设备过早失效。白色中子束——表面上是最具代表性的 SEE 测试方法——通常来自基于固体靶的源,导致通量不均匀和光束面积较小。白色中子束的能谱也具有一定的不确定性,通常具有较高的热中子含量。

使用单能 14 MeV 中子进行 SEE 测试可以避免质子和散裂中子源的缺点。一个潜在的问题是单能中子引起的单粒子效应不能准确地代表广谱大气中子在现实世界中的影响。然而,最近的研究表明,事实恰恰相反,单能中子(特别是 14 MeV 中子)可以用来相当准确地理解现代微电子学中的 SEE 截面。 [9]

抗辐射技术

[编辑]

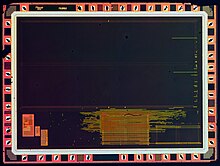

物理上

[编辑]抗辐射芯片不使用半导体晶圆,通常是在绝缘基板上制造。常见的有使用SOI (绝缘体上的硅晶体管结构)或 SOS(蓝宝石上的硅晶体管结构 )。普通商用级芯片可承受 50 至 100戈瑞(5 至 10 千拉德),而航太级 SOI 和 SOS 芯片可承受 1000 至 3000戈瑞(100 至 300 千拉德)的剂量。 [10] [11]许多4000 系列芯片都曾提供抗辐射版本(RadHard)。 [12]虽然 SOI 可以消除闩锁事件,但不能保证对于 TID 和 SEE 的抗性会得到改善。 [13]

双极集成电路通常比CMOS电路具有更高的辐射耐受性。低功耗肖特基 (LS) 5400 系列可承受 1000 krad,许多ECL 元件可承受 10 000 krad。 [12]

磁阻RAM ( MRAM )被认为是提供抗辐射、可重写、非易失性导体存储器的可能候选者。物理原理和早期测试表明,MRAM 不易受到电离引起的数据丢失的影响。 [14]

基于电容器的DRAM经常被更坚固(但更大、更昂贵)的 SRAM所取代。

选择宽带隙的衬底,使其对深能级缺陷具有更高的耐受性;例如碳化硅或氮化镓。[来源请求]</link>[需要引用]

遮蔽包装以防止放射性物质的暴露,从而减少裸露设备的暴露。 [15]

通过在保护芯片的硼磷硅酸盐玻璃钝化层中使用贫化硼(仅由同位素硼-11组成)来遮蔽芯片本身(免受中子的影响),因为自然界中普遍存在的硼-10很容易捕获中子并发生α衰变(参见软错误)。

采用特殊制程技术节点以提高抗辐射能力。 [16]由于新型抗辐射制程的开发成本较高,1950 年代中期已经出现采用“真正的”抗辐射制程(RHBD,Rad-Hard By Design)的抗辐射 65 奈米 FPGA 。截至 2016 年“真正的”最小抗辐射制程(RHBP,Rad-Hard By Process)为 150奈米。 [17]截至 2019 年 110奈米抗辐射制程已经问世。 [18]

使用比通常更多的晶体管(4T 或 6T)的 SRAM 单元,这使得单元对 SEU 的耐受性更强,但代价是更高的功耗和每个单元的尺寸。 [19] [17]

使用无边缘 CMOS晶体管,这种晶体管具有非常规的物理结构和非传统的物理布局。 [20]

逻辑上

[编辑]错误纠正代码内存(ECC 内存)使用冗余位来检查并可能纠正损坏的数据。由于即使系统未访问 RAM,辐射效应也会损坏内存内容,因此“清除器”电路必须不断扫描 RAM;读出数据,检查冗余位是否存在数据错误,然后将所有更正内容写回 RAM。

可以在系统级使用冗余元素。三个独立的微处理器板可以独立地计算出一个计算的答案并比较它们的答案。任何产生少数结果的系统都将重新计算。可以添加逻辑,这样如果同一系统出现重复错误,则该板就会关闭。

可以在电路级使用冗余元件。 [21]可以将单个位替换为三个位,并为每个位分配单独的“投票逻辑”以连续确定其结果(三重模块冗余)。这使得芯片设计的面积增加了 5 倍,因此必须保留用于较小的设计。但它的另一个优点就是还能即时保证“故障安全”。如果发生单位故障(可能与辐射无关),投票逻辑将继续产生正确的结果,而无需借助看门狗定时器。三个独立处理器系统之间的系统级投票通常需要使用一些电路级投票逻辑来执行三个处理器系统之间的投票。

可以使用抗辐射闩锁。 [22]

看门狗定时器将执行系统的硬重置,除非执行某些通常表明系统处于活动状态的序列,例如来自板载处理器的写入操作。在正常运行期间,软件会定期安排对看门狗定时器的写入,以防止定时器耗尽。如果辐射导致处理器运行不正常,则软件不太可能正常工作以清除看门狗定时器。看门狗最终会超时并强制对系统进行硬重置。这被认为是其他辐射硬化方法的最后手段。

军事和航太工业应用

[编辑]抗辐射和耐辐射组件通常用于军事和航太应用,包括负载点(POL)应用、卫星系统电源、降压开关稳压器、微处理器、 FPGA 、 [23] FPGA电源和高效、低压子系统电源。

然而,并非所有军用级组件都具有抗辐射性能。例如,美国MIL-STD-883有许多与辐射相关的测试,但没有对单粒子闩锁频率的规范。 Fobos-Grunt太空探测器可能由于类似的假设而失败。 [13]

预计 2021 年用于太空应用的抗辐射电子产品的市场规模将达到 23.5 亿美元。一项新研究估计,到 2032 年,这一数位将达到约 47.6 亿美元。 [24] [25]

电信核抗性

[编辑]在电信领域中,核硬度一词有以下含义:1)表示系统、设施或设备的性能在给定的核环境中预计会下降的程度;2)系统或电子元件的物理属性,使其能够在包括核辐射和电磁脉冲 (EMP) 的环境中生存。

备注

[编辑]- 核抗性可以用敏感度或脆弱度来表示。

- 必须定义或指定预期性能下降的程度(例如,停机时间、数据丢失和设备损坏)。必须定义或指定环境(例如辐射水平、过压、峰值速度、吸收能量和电应力)。

- 系统或部件的物理属性,可在核武器造成的特定环境下实现一定程度的生存能力。

- 核抗性是根据规定或实际量化的环境条件和物理参数来确定的,例如峰值辐射水平、过压、速度、吸收能量和电应力。它是通过设计规范实现的,并通过测试和分析技术进行验证。

抗辐射电脑示例

[编辑]- The System/4 Pi, made by IBM and used on board the Space Shuttle (AP-101 variant), is based on the System/360 architecture.

- The RCA1802 8-bit CPU, introduced in 1976, was the first serially-produced radiation-hardened microprocessor.

- PIC 1886VE, Russian 50 MHz microcontroller designed by Milandr and manufactured by Sitronics-Mikron on 180 nm bulk-silicon technology.

- m68k based:

- The Coldfire M5208 used by General Dynamics is a low power (1.5 W) radiation hardened alternative.

- MIL-STD-1750A based:

- The RH1750 manufactured by GEC-Plessey.

- The Proton 100k SBC by Space Micro Inc., introduced in 2003, uses an updated voting scheme called TTMR which mitigates single event upset (SEU) in a single processor. The processor is Equator BSP-15.[来源请求][citation needed]

- The Proton200k SBC by Space Micro Inc, introduced in 2004, mitigates SEU with its patented time triple modular redundancy (TTMR) technology, and single event function interrupts (SEFI) with H-Core technology. The processor is the high speed Texas Instruments 320C6Xx series digital signal processor. The Proton200k operates at 4000 MIPS while mitigating SEU.[来源请求][citation needed]

- MIPS based:

- The RH32 is produced by Honeywell Aerospace.

- The Mongoose-V used by NASA is a 32-bit microprocessor for spacecraft onboard computer applications (i. e. New Horizons).

- The KOMDIV-32 is a 32-bit microprocessor, compatible with MIPS R3000, developed by NIISI, manufactured by Kurchatov Institute, Russia.

- PowerPC / POWER based:

- The RAD6000 single-board computer (SBC), produced by BAE Systems, includes a rad-hard POWER1 CPU.

- The RHPPC is produced by Honeywell Aerospace. Based on hardened PowerPC 603e.

- The SP0 and SP0-S are produced by Aitech Defense Systems is a 3U cPCI SBC which utilizes the SOI PowerQUICC-III MPC8548E, PowerPC e500 based, capable of processing speeds ranging from 833 MHz to 1.18 GHz.[26]

- The RAD750 SBC, also produced by BAE Systems, and based on the PowerPC 750 processor, is the successor to the RAD6000.

- The SCS750 built by Maxwell Technologies, which votes three PowerPC 750 cores against each other to mitigate radiation effects. Seven of those are used by the Gaia spacecraft.

- The Boeing Company, through its Satellite Development Center, produces a radiation hardened space computer variant based on the PowerPC 750.

- The BRE440 by Broad Reach Engineering. IBM PPC440 core based system-on-a-chip, 266 MIPS, PCI, 2x Ethernet, 2x UARTS, DMA controller, L1/L2 cache

- The RAD5500 processor, is the successor to the RAD750 based on the PowerPC e5500.

- SPARC based:

- The ERC32 and LEON 2, 3, 4 and 5 are radiation hardened processors designed by Gaisler Research and the European Space Agency. They are described in synthesizable VHDL available under the GNU Lesser General Public License and GNU General Public License respectively.

- The Gen 6 single-board computer (SBC), produced by Cobham Semiconductor Solutions (formerly Aeroflex Microelectronics Solutions), enabled for the LEON microprocessor.[27]

- ARM based:

- RISC-V based:

- Cobham Gaisler NOEL-V 64-bit.[30]

- NASA Jet Propulsion Laboratory has selected Microchip Technology to develop a new HPSC processor, based on SiFive Intelligence X280[31][32][33]

参见

[编辑]- ^ Messenger, George C. Radiation hardening. AccessScience. doi:10.1036/1097-8542.566850.

- ^ Quantum computers may be destroyed by high-energy particles from space. New Scientist. [7 September 2020]. (原始内容存档于2024-07-11).

- ^ Cosmic rays may soon stymie quantum computing. phys.org. [7 September 2020] (英语).

- ^ Vepsäläinen, Antti P.; Karamlou, Amir H.; Orrell, John L.; Dogra, Akshunna S.; Loer, Ben; Vasconcelos, Francisca; Kim, David K.; Melville, Alexander J.; Niedzielski, Bethany M.; Yoder, Jonilyn L.; Gustavsson, Simon. Impact of ionizing radiation on superconducting qubit coherence. Nature. August 2020, 584 (7822): 551–556 [7 September 2020]. Bibcode:2020Natur.584..551V. ISSN 1476-4687. PMID 32848227. S2CID 210920566. arXiv:2001.09190

. doi:10.1038/s41586-020-2619-8. (原始内容存档于2021-10-14) (英语).

. doi:10.1038/s41586-020-2619-8. (原始内容存档于2021-10-14) (英语).

- ^ Ziegler, J. F.; Lanford, W. A. Effect of Cosmic Rays on Computer Memories. Science. 16 November 1979, 206 (4420): 776–788. Bibcode:1979Sci...206..776Z. PMID 17820742. S2CID 2000982. doi:10.1126/science.206.4420.776.

- ^ Ziegler, J. F.; Lanford, W. A. The effect of sea level cosmic rays on electronic devices. Journal of Applied Physics. June 1981, 52 (6): 4305–4312. Bibcode:1981JAP....52.4305Z. doi:10.1063/1.329243.

- ^ Brugger, M. Radiation Damage to Electronics at the LHC. 3rd International Particle Accelerator Conference. New Orleans, Louisiana: THPPP006. May 2012 [2024-06-01]. (原始内容存档于2024-06-01).

- ^ Messenger, G.C.; Ash, Milton. Single Event Phenomena. Springer Science & Business Media. 2013-11-27: xii–xiii. ISBN 978-1-4615-6043-2.

- ^ Normand, Eugene; Dominik, Laura. 2010 IEEE Radiation Effects Data Workshop. 2010 IEEE Radiation Effects Data Workshop: 8. 20–23 July 2010. ISBN 978-1-4244-8405-8. doi:10.1109/REDW.2010.5619496.

- ^ Microsemi Corporation, RTSX-SU Radiation-Tolerant FPGAs (UMC) (PDF) (Datasheet), March 2012 [May 30, 2021], (原始内容存档 (PDF)于2022-01-26)

- ^ Atmel Corporation, Rad Hard 16 MegaBit 3.3V SRAM MultiChip Module AT68166H (PDF) (Datasheet), 2008 [May 30, 2021], (原始内容存档 (PDF)于2023-12-23)

- ^ 12.0 12.1 Leppälä, Kari; Verkasalo, Raimo. Protection of Instrument Control Computers against Soft and Hard Errors and Cosmic Ray Effects. International Seminar on Space Scientific Engineering. 17–23 September 1989. CiteSeerX 10.1.1.48.1291

.

.

- ^ 13.0 13.1 Shunkov, >V. Common misconceptions about space-grade integrated circuits. habr.com (英语).

- ^ Wang, B.; Wang, Z.; Hu, C.; Zhao, Y.; Zhang, Y.; Zhao, W. 2018 IEEE International Magnetics Conference (INTERMAG). 2018 IEEE International Magnetics Conference (INTERMAG): 1–2. 2018. ISBN 978-1-5386-6425-4. doi:10.1109/INTMAG.2018.8508368.

- ^ StackPath. [2024-06-01]. (原始内容存档于2022-11-18).

- ^ The other Atmel: Radiation Hardened Sparc CPU's | the CPU Shack Museum. 27 July 2009 [2024-06-01]. (原始内容存档于2024-04-20).

- ^ 17.0 17.1 Avnet: Quality Electronic Components & Services (PDF).

- ^ Aerospace & Defense Solutions (PDF). Onsemi. [2024-06-01]. (原始内容存档 (PDF)于2022-07-19).

- ^ Tiehu Li; Yintang Yang; Junan Zhang; Jia Liu. A novel SEU hardened SRAM bit-cell design. IEICE Electronics Express: 1–8.

- ^ Benigni, Marcello; Liberali, Valentino; Stabile, Alberto; Calligaro, Cristiano. Design of rad-hard SRAM cells: A comparative study. 27th International Conference on Microelectronics Proceedings. 2010. doi:10.1109/miel.2010.5490481.

- ^ Platteter, Dale G. Protection of LSI Microprocessors using Triple Modular Redundancy. International IEEE Symposium on Fault Tolerant Computing. October 1980.

- ^ Krishnamohan, Srivathsan; Mahapatra, Nihar R. Proceedings of the 15th ACM Great Lakes symposium on VLSI - GLSVSLI '05. Proceedings of the 15th ACM Great Lakes symposium on VLSI: 328. 2005. ISBN 1595930574. doi:10.1145/1057661.1057740.

- ^ Mil & Aero Staff. FPGA development devices for radiation-hardened space applications introduced by Microsemi. Military & Aerospace Electronics. 2016-06-03 [2018-11-02].

- ^ Diagle, Lisa. Rad-hard electronics for space to reach $4.76 billion by 2032, study says. Military Embedded Systems. 2022-06-17 [2022-06-18].

- ^ https://www.researchandmarkets.com/reports/5589889/radiation-hardened-electronics-for-space

- ^ SP0 3U CompactPCI Radiation Tolerant PowerPC® SBC. Aitech Rugged COTS Solutions . 2013-12-15. (原始内容存档于2014-06-23).

- ^ Single Board Computer (SBC) Family. Cobham. [2018-11-02]. (原始内容存档于2019-04-08).

- ^ VA10820 - Radiation Hardened ARM Cortex-M0 MCU. Vorago Technologies. [2018-11-02]. (原始内容存档于2019-02-14).

- ^ Powell, Wesley A. High-Performance Spaceflight Computing (HPSC) Project Overview (PDF). NASA Technical Reports Server (NTRS) (报告). 2018-11-13 [2024-06-01]. (原始内容存档 (PDF)于2024-06-23).

- ^ NOEL-V Processor. Cobham Gaisler. [14 January 2020].

- ^ NASA Makes RISC-V the Go-to Ecosystem for Future Space Missions. sifive. 2022-09-22.

- ^ NASA JPL Selects Microchip for Game-Changing Spaceflight Computing Processor. microchip. 2022-09-27.

- ^ NASA Awards Next-Generation Spaceflight Computing Processor Contract. nasa. 2022-08-15 [2024-06-01]. (原始内容存档于2024-07-17).

参考资料

[编辑]书籍和报告

[编辑]- Calligaro, Christiano; Gatti, Umberto. Rad-hard Semiconductor Memories. River Publishers Series in Electronic Materials and Devices. River Publishers. 2018. ISBN 978-8770220200.

- Holmes-Siedle, Andrew; Adams, Len. Handbook of Radiation Effects Second. Oxford University Press. 2002. ISBN 0-19-850733-X.

- León-Florian, E.; Schönbacher, H.; Tavlet, M. Data compilation of dosimetry methods and radiation sources for material testing (报告). CERN Technical Inspection and Safety Commission. 1993. CERN-TIS-CFM-IR-93-03.

- Ma, Tso-Ping; Dressendorfer, Paul V. Ionizing Radiation Effects in MOS Devices and Circuits. New York: John Wiley & Sons. 1989. ISBN 0-471-84893-X.

- Messenger, George C.; Ash, Milton S. The Effects of Radiation on Electronic Systems Second. New York: Van Nostrand Reinhold. 1992. ISBN 0-442-23952-1.

- Oldham, Timothy R. Ionizing Radiation Effects in MOS Oxides. International Series on Advances in Solid State Electronics and Technology. World Scientific. 2000. ISBN 978-981-02-3326-6. doi:10.1142/3655.

- Platteter, Dale G. Archive of Radiation Effects Short Course Notebooks (1980–2006). IEEE. 2006. ISBN 1-4244-0304-9.

- Schrimpf, Ronald D.; Fleetwood, Daniel M. Radiation Effects and Soft Errors in Integrated Circuits and Electronic Devices. Selected Topics in Electronics and Systems 34. World Scientific. July 2004. ISBN 978-981-238-940-4. doi:10.1142/5607.

- Schroder, Dieter K. Semiconductor Material and Device Characterization. New York: John Wiley & Sons. 1990. ISBN 0-471-51104-8.

- Schulman, James Herbert; Compton, Walter Dale. Color Centers in Solids. International Series of Monographs on Solid State Physics 2. Pergamon Press. 1962.

- Holmes-Siedle, Andrew; van Lint, Victor A. J. Meyers, Robert A. , 编. Radiation Effects in Electronic Materials and Devices 13 Third. New York: Academic Press. 2000. ISBN 0-12-227423-7.

- van Lint, Victor A. J.; Flanagan, Terry M.; Leadon, Roland Eugene; Naber, James Allen; Rogers, Vern C. Mechanisms of Radiation Effects in Electronic Materials. NASA Sti/Recon Technical Report A 1 (New York: John Wiley & Sons). 1980: 13073. Bibcode:1980STIA...8113073V. ISBN 0-471-04106-8.

- Watkins, George D. Pantelides, Sokrates T. , 编. The Lattice Vacancy in Silicon Second. New York: Gordon and Breach. 1986. ISBN 2-88124-109-3.

- Watts, Stephen J. Overview of radiation damage in silicon detectors — Models and defect engineering. Nuclear Instruments and Methods in Physics Research Section A. 1997, 386 (1): 149–155. Bibcode:1997NIMPA.386..149W. doi:10.1016/S0168-9002(96)01110-2.

- Ziegler, James F.; Biersack, Jochen P.; Littmark, Uffe. The Stopping and Range of Ions in Solids 1. New York: Pergamon Press. 1985. ISBN 0-08-021603-X.

外部链接

[编辑]- 联邦标准 1037C (链接互联网档案馆的存档,存档日期2011-03-01.</link> )

- 采用 COTS 的集成方法为太空打造抗辐射 (SBC) 技术– 作者:Chad Thibodeau,Maxwell Technologies; COTS 杂志,2003 年 12 月

- 桑迪亚实验室将开发 (...) 抗辐射奔腾 (...),以满足太空和国防需求 (页面存档备份,存于互联网档案馆)– 桑迪亚新闻稿,1998 年 12 月 8 日

</br>(还包括有关桑迪亚国家实验室微电子辐射硬化制造制程的一般“背景资料”部分) - 辐射对石英晶体的影响

- 范德比尔特大学空间与国防电子研究所