在數位電路理論中,組合邏輯電路(英語:Combinatorial logic, combinational logic)是一種邏輯電路,它的任一時刻的穩態輸出,僅僅與該時刻的輸入變量的取值有關,而與該時刻以前的輸入變量取值無關。相對於組合邏輯電路,序向邏輯電路的輸出結果除了依照目前的輸入外也和先前的輸入有關係。從電路結構分析,組合電路由各種邏輯閘組成,網絡中無記憶元件,也無回饋線。

組合邏輯是在電腦被用來做輸入的訊號跟儲存的資料作邏輯代數運算之用。實際上電腦電路都會混用包含組合邏輯和時序邏輯的電路。舉例來說,算術運算邏輯單元(ALU)中,儘管ALU是由循序邏輯的程式裝置所控制,而數學的運算就是從組合邏輯製產生的。計算機中用到的其他電路,如半加器、全加器、半減器、全減器、數據多工器、數據分配器、編碼器和解碼器也用來構成組合邏輯電路。

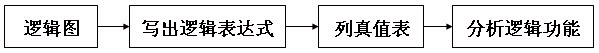

由已知的邏輯電路圖,找出輸入變量和輸出函數之間的邏輯關係,達到分析電路功能,評價設計好壞,維護系統硬體,改善電路設計的目的,這個過程稱為數位電路的邏輯分析。

組合電路分析的步驟:

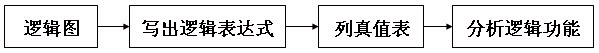

邏輯設計又稱為邏輯綜合,根據給定的邏輯條件或者提出的邏輯功能,整理出滿足該邏輯的電路,這個過程稱為數位電路的邏輯設計。

組合邏輯系統的實際設計可能要考慮實際邏輯元件對輸入變化作出反應的時間。輸出是由多個不同路徑、不同時亮的開關元件組合而成時,由於變化沿不同路徑傳播,輸出在穩定到穩態之前可能會發生瞬間改變。[1]

組合邏輯的構建通常是兩種方法之一:積之和,或和之積。考慮以下真值表:

| A |

B |

C |

輸出 |

邏輯等價

|

| F |

F |

F |

F |

|

| F |

F |

T |

F |

|

| F |

T |

F |

F |

|

| F |

T |

T |

F |

|

| T |

F |

F |

T |

|

| T |

F |

T |

F |

|

| T |

T |

F |

F |

|

| T |

T |

T |

T |

|

用乘積相加法,將所有輸出真的語句相加:

運用布林代數,輸出可簡化為真值表的等價:

組合邏輯公式的最小化(簡化)通過以下基於布林代數運算律的規則完成:

最小化(邏輯優化)可以得到簡化的邏輯函數或電路,從而使邏輯組合電路變得更小、更易於分析、使用或構建。

組合電路設計的步驟:

- ^ Lewin, Douglas. Logical Design of Switching Circuits 2nd. Thomas Nelson and Sons. 1974: 162–3. ISBN 017-771044-6.